浅聊 esp8266

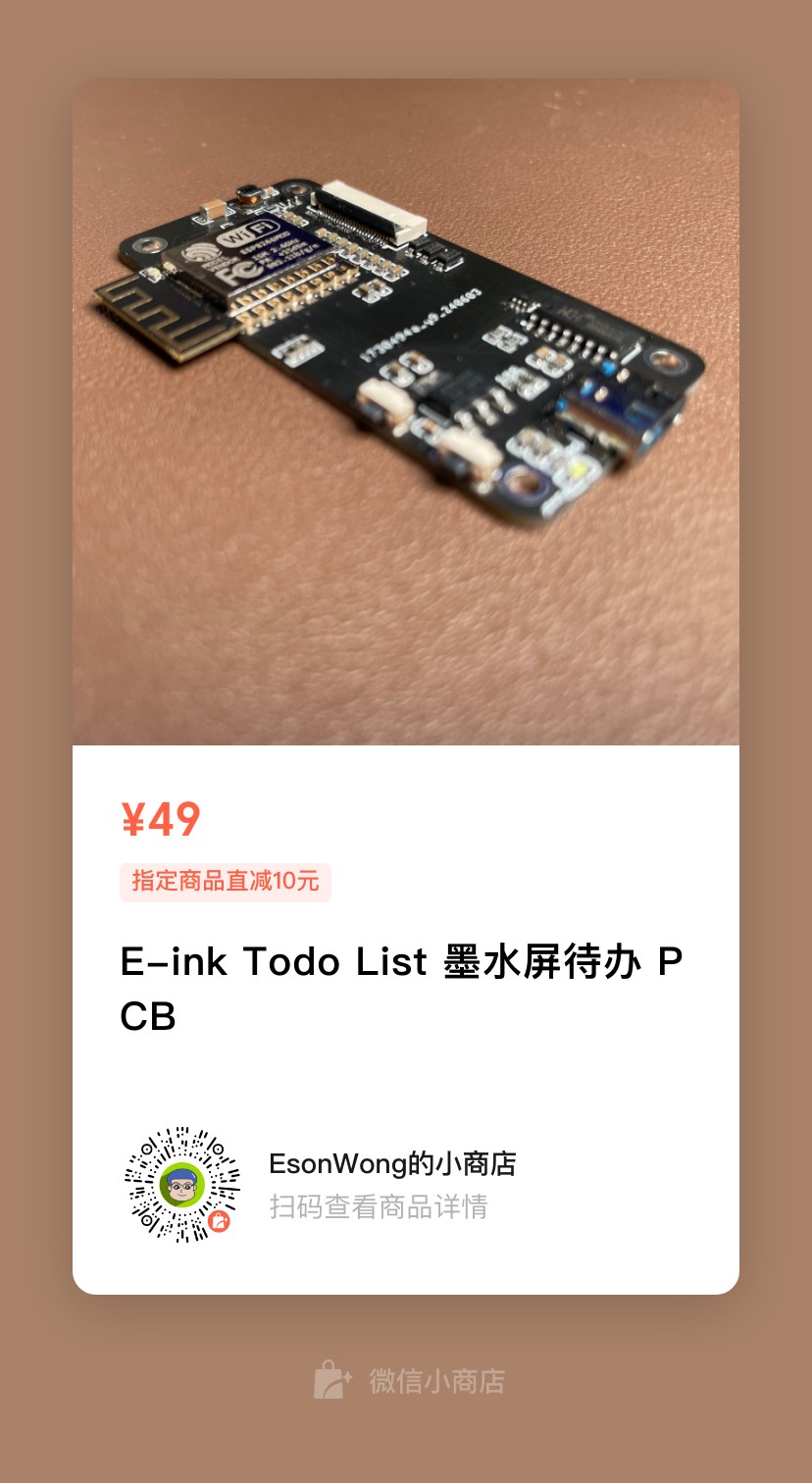

最近在做 E-ink Todo List 项目,用到了 ESP8266,所以就简单的聊一下 ESP8266。

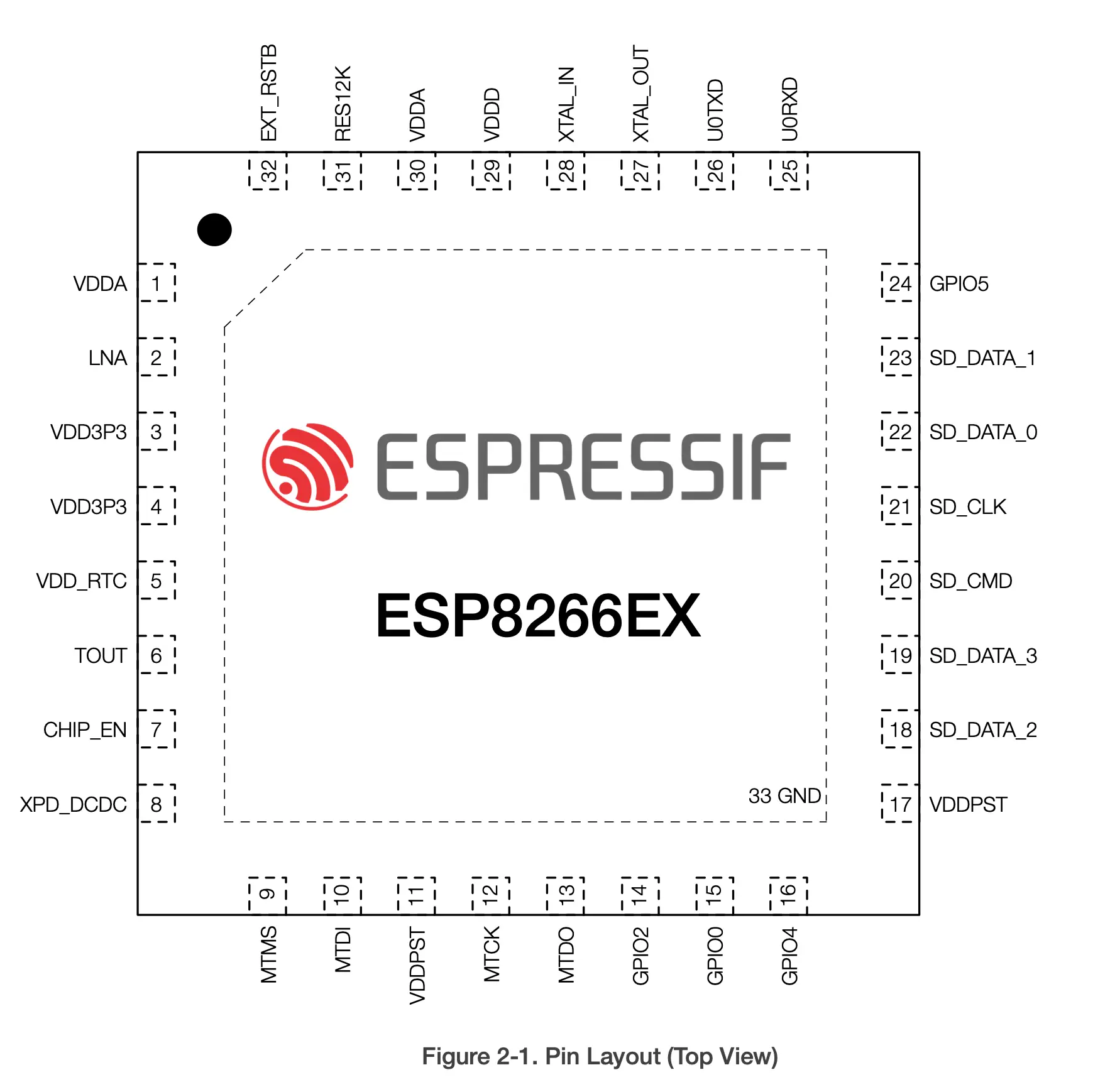

ESP8266EX

ESP8266 是由乐鑫科技推出的一个芯片系列,ESP8266EX 是其中的一款。

ESP8266EX 提供了完整 TCP/IP 协议栈和 WiFi 功能,一个 10 位 ADC,支持 SPI、I2C、UART、PWM 等接口。是一个非常适合用于做一些需要无线联网且由电池供电的项目的芯片。

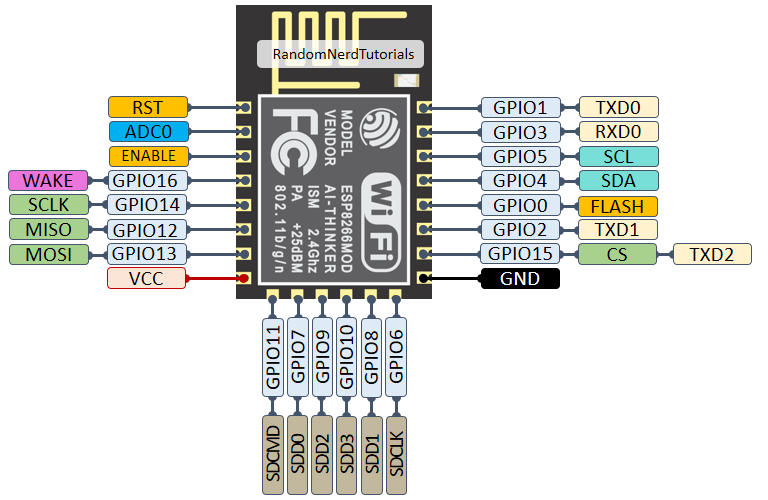

ESP-12F 模组

为了快速创造我想要的东西,我使用了安可信的 ESP-12F 模组。使用 SMD 封装方式。它集成了 ESP8266EX 芯片,WiFi 天线和外部闪存的模组。

SMD 是 Surface-Mounted Device(表面贴装设备)的缩写。起源于 1960 年代,最初由美国 IBM 公司进行技术研发,之后于 1980 年代后期渐趋成熟。它的特点是元件直接贴装在电路板的表面,而不需要通过电路板的孔进行焊接。这种封装方式使得元件可以更小,更轻,而且可以在电路板的两面进行贴装。SMD0805 和 SMD0603 是常见的 SMD 封装规格,0805 封装的尺寸是 0.08 英寸 x 0.05 英寸( 2.0mm x 1.25mm),0603 封装的尺寸是 0.06 英寸 x 0.03 英寸(1.6mm x 0.8mm)。

ESP-12F 是特殊尺寸的 SMD 封装。

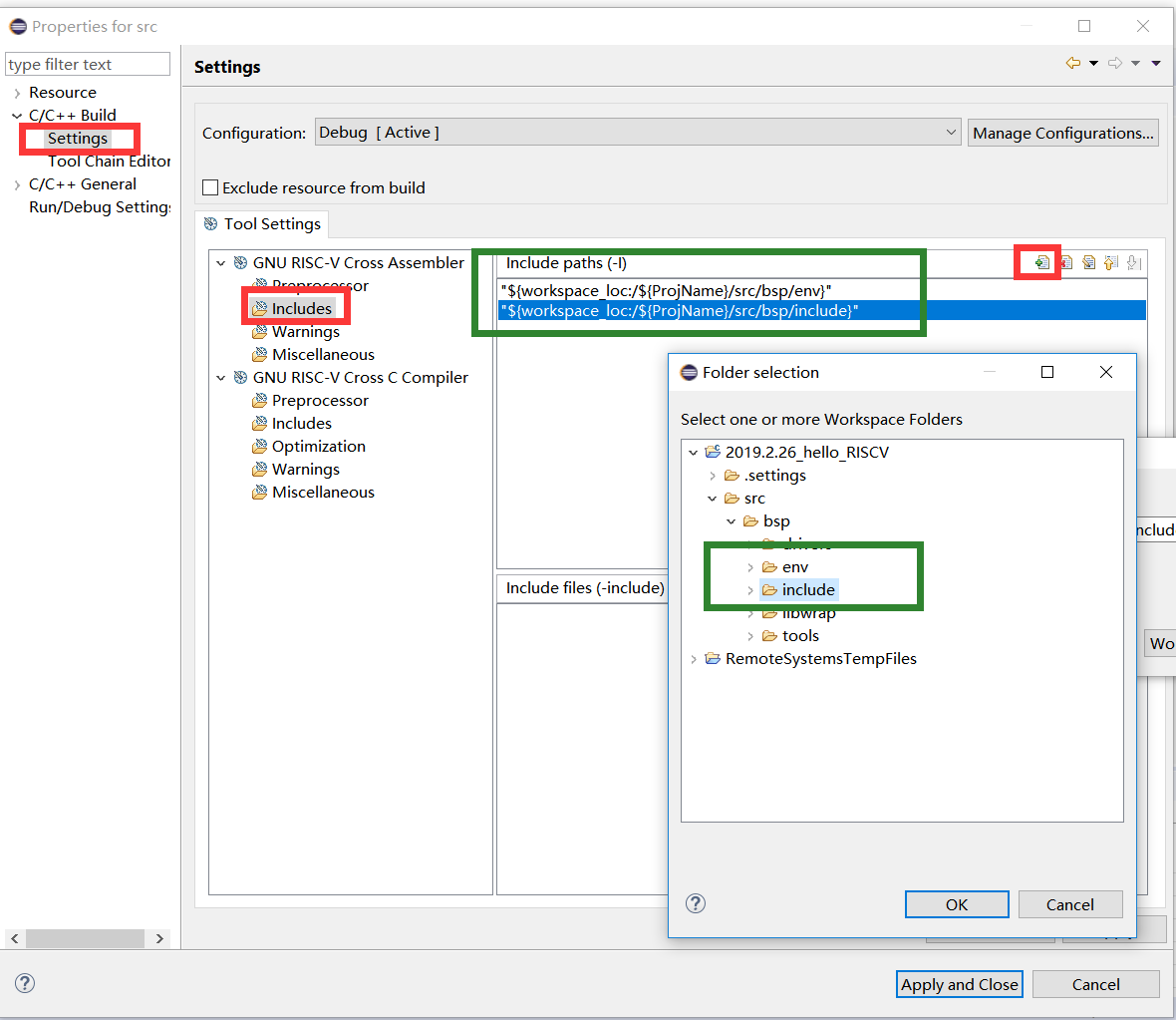

固件下载

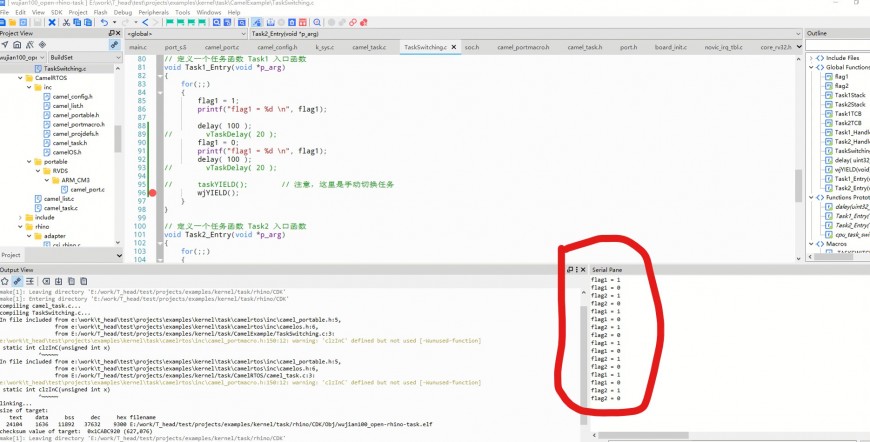

项目中用了 USB 转 TTL 串口芯片 CH340C 通过下面的引脚来实现自动下载固件和进入运行模式。

ENABLE

使能引脚,当使能引脚为高电平时,芯片或模块处于工作状态;当使能引脚为低电平时,芯片或模块处于待机或关断状态。

GPIO0(FLASH)

用于控制 ESP8266EX 进入下载模式。当 GPIO0 为低电平时, 让 ENABLE 引脚上升沿(从低电平到高电平)时,ESP8266EX 将进入下载模式。当 ESP8266EX 处于运行模式时,GPIO0 引脚可作为普通的输入输出引脚使用。

GPIO1(TX)

UART 通用串口通讯的接收引脚

GPIO3(RX)

UART 通用串口通讯的接收引脚

我会单独写一篇文章详细介绍自动下载电路的原理。

SPI 电路

SPI(Serial Peripheral Interface) 是一种芯片与芯片的外围设备通信协议。需要用到 4 条线路,分别是:

SCK(Serial Clock)

串行时钟信号,由主设备产生,用于对齐数据传输的间隔。

MOSI(Master Out Slave In)

主设备输出,从设备输入,主设备发送数据到从设备。

MISO(Master In Slave Out)

主设备输入,从设备输出,从设备发送数据到主设备。

SS(Slave Select) 或 CS(Chip Select)

从设备选择信号,由主设备产生,用于选择从设备。

我在项目中使用 SPI 通信方式与 E-ink 屏幕通信。除了上面的 4 条线路外,还用要控制 E-ink 屏幕的复位,以及读取 E-ink 屏幕是否忙碌的状态。

我在 ESP-12F 上使用了下面的引脚:

| ESP-12F | E-ink 驱动电路 | 功能 |

|---|---|---|

| GPIO2 | RST | 控制屏幕复位的引脚,低电平复位屏幕 |

| GPIO4 | DC | 控制引脚屏幕的数据和命令模式,高电平表示数据,低电平表示命令 |

| GPIO5 | BUSY | 屏幕忙碌状态输出引脚,高电平表示屏幕忙碌,低电平表示屏幕空闲 |

| GPIO13(MOSI) | DIN | SPI 通信 MOSI 引脚 |

| GPIO14(SCK) | CLK | SPI 通信 SCK 引脚 |

| GPIO15(CS) | CS | SPI 片选引脚 |

ADC 引脚

ESP-12F 有一个 10 位 ADC,可以用来读取模拟量信号。我将会用这个引脚来读取电池电压。ADC0 引脚可读取 0-1V 的电压。需要使用一个电阻分压电路将电池电压分压到 0-1V 范围内再通过 ADC0 引脚读取。

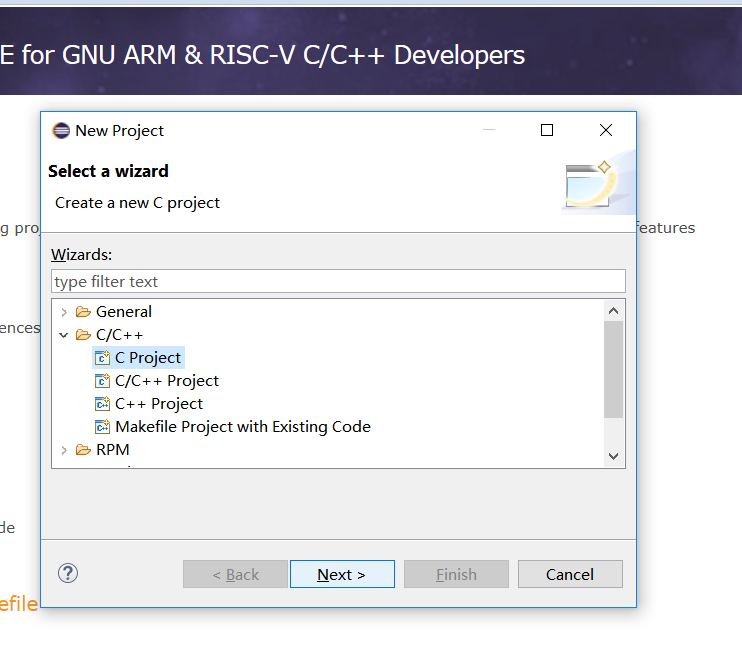

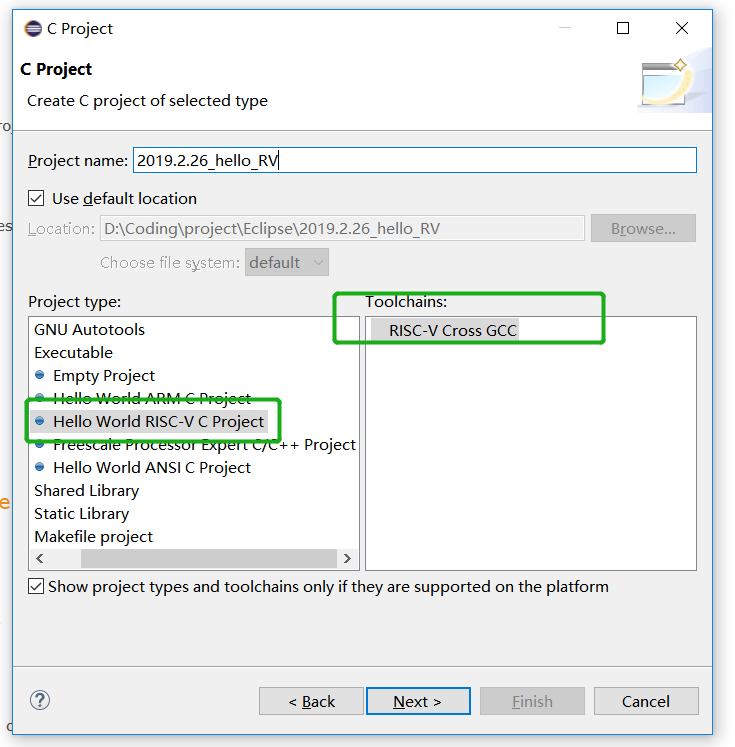

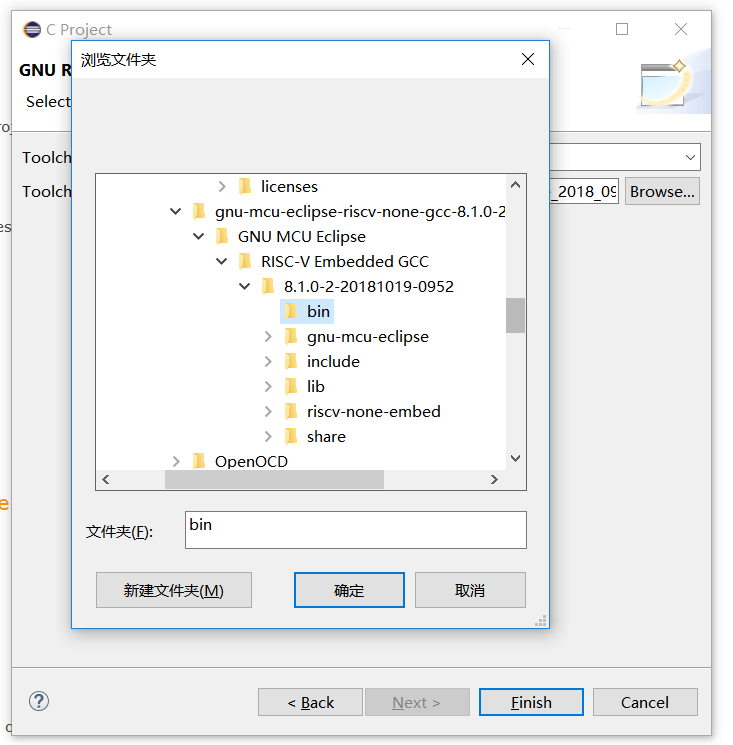

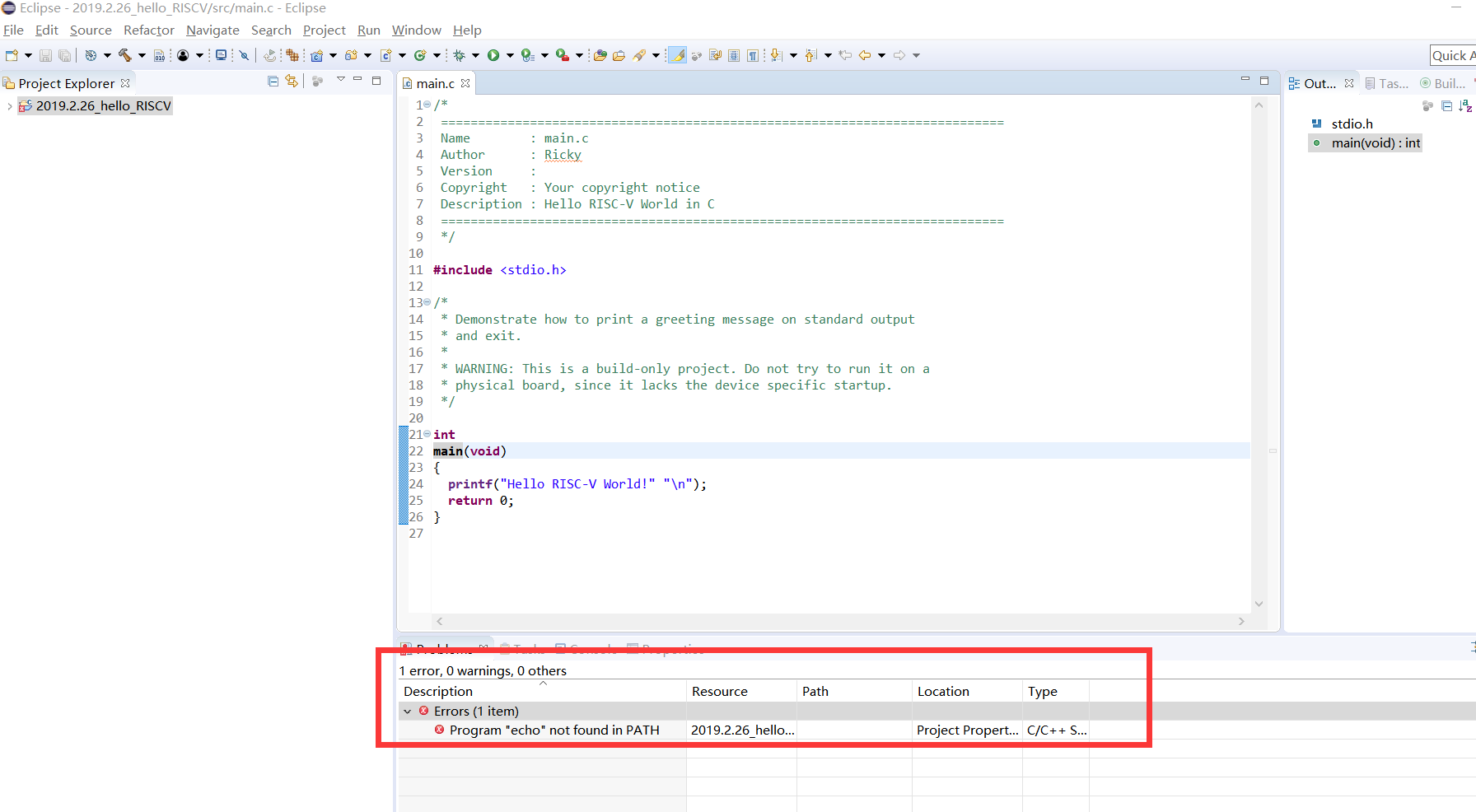

编程平台

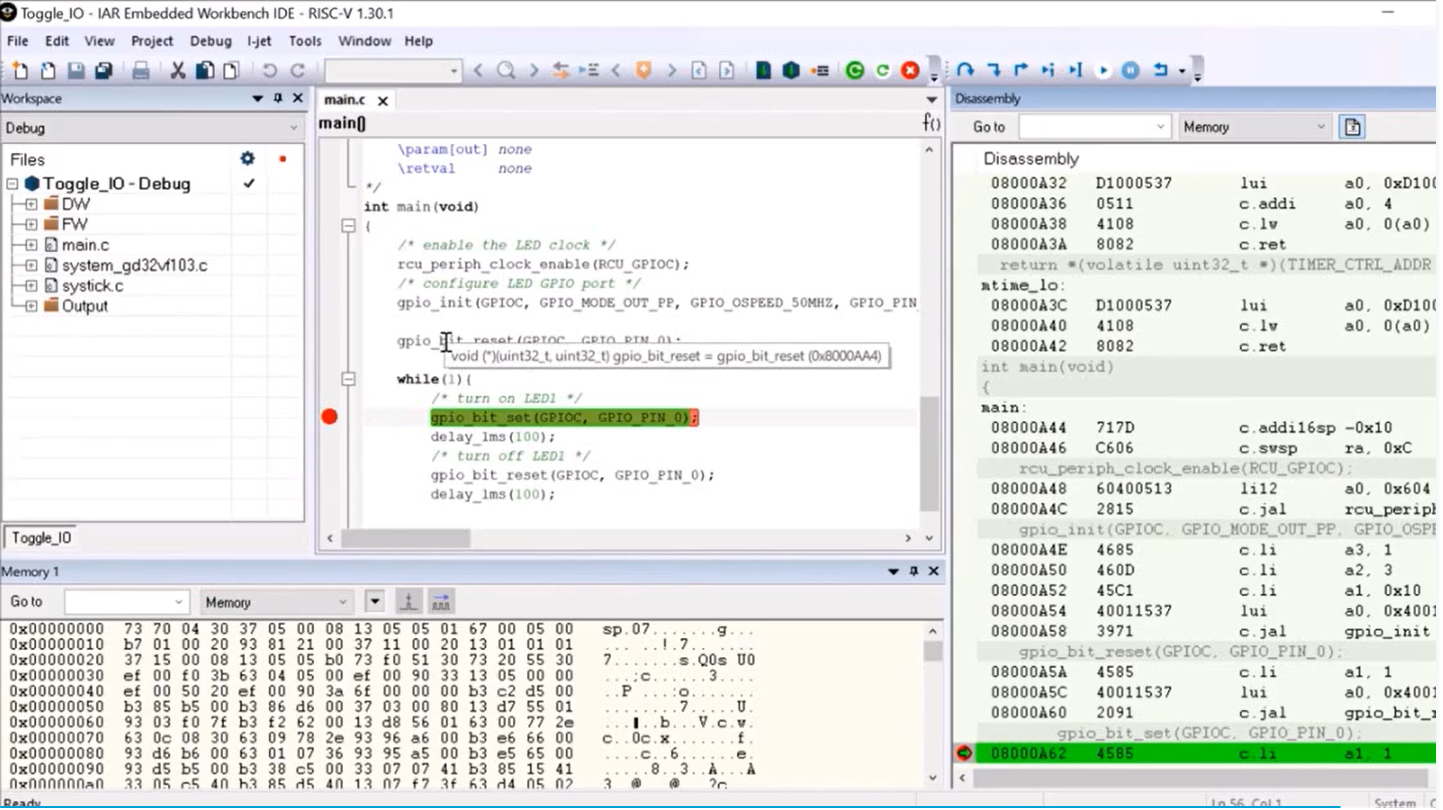

ESP8266EX 的开发环境有很多,我选择了 PlatformIO。一开始我是使用 Arduino IDE 来开发的,但是 Arduino IDE 的功能太过简单,不适合太复杂的项目。

我使用 VSCode 安装了 PlatformIO 插件,通过 PlatformIO 的 CLI 工具来编译和下载固件。

参考

广告

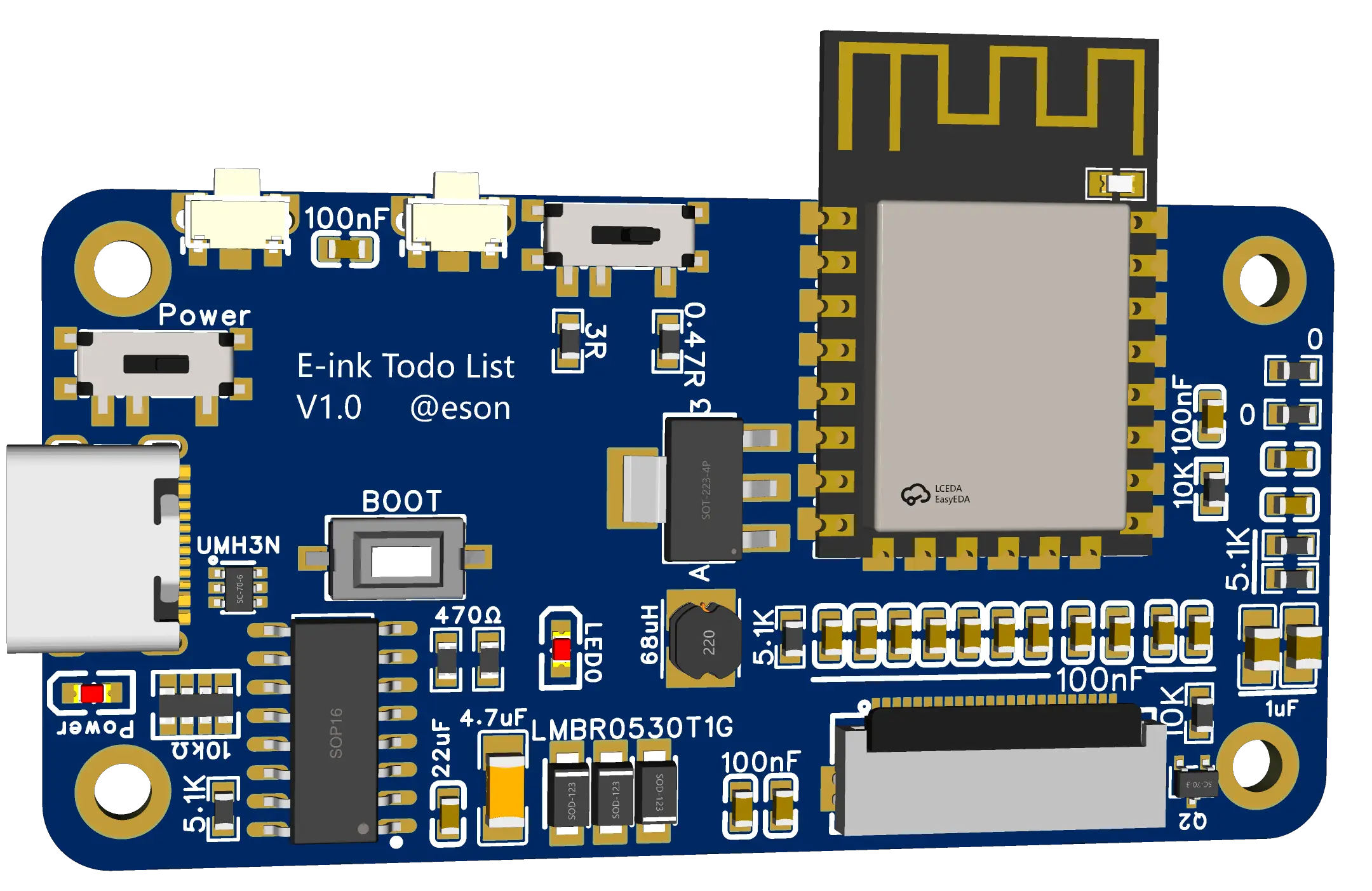

本文由我在制作 E-ink Todo List 墨水屏待办 DIY 的 PCB 板时总结的,我还写了一篇《墨水屏 Todo List 制作教程》。

👋 E-ink Todo List 墨水屏待办 DIY 的 PCB 现已上架售卖 😇,此 PCB 板可代替教程中的开发板和屏幕转接板。爱好 DIY 的朋友们可以下单购买制作。

E-ink Todo List 墨水屏待办的成品正在起来的路上!!!

下面是 PCB 板的购买途径。

EsonWong 的微信小店